For hardware startups and OEMs, getting high-quality PCBs quickly and reliably is critical. MC PCB is a one-stop contract PCB manufacturer supporting prototypes to volume builds—backed by experienced engineering support and rigorous QA.

-

No. 2, Lane 11, Wenming Road, Fourth Industrial Zone, Nanzha, Humen Town, Dongguan City

How do different PCB stackups affect impedance at high frequencies?

See how PCB stackups change impedance at high frequencies. Compare microstrip vs stripline, Dk/Df, planes, pours, and tolerances so links stay clean.

Table of Contents

At high frequency, your trace isn’t “just copper.” It’s a transmission line, and the PCB stackup is the environment that shapes its electric fields. If the stackup shifts, impedance shifts. That’s when you see the usual headaches: eye diagram collapse, random EMI spikes, failed RF match, or a “works on the bench, dies in the enclosure” prototype.

If you build for OEM/ODM, EMS, design houses, or startup hardware teams, you already know the pattern: layout looks clean, but the line doesn’t behave like the calculator promised. Stackup is often the hidden root cause.

This guide walks through the core stackup decisions that move impedance around at high frequencies—using real manufacturing language (DFM, coupons, TDR, etch comp) instead of theory-only talk.

Microstrip vs stripline: stackup geometry sets the transmission line

When you pick a signal layer, you’re also picking the transmission-line type:

- Microstrip: outer-layer trace over a reference plane

- Stripline: inner-layer trace sandwiched between planes

Why you care: microstrip fields live partly in air and partly in dielectric. Stripline fields sit mostly inside the dielectric. That changes the effective dielectric constant, which changes characteristic impedance (Z0) and propagation behavior.

Real-world pain point: teams move a “50 Ω” net from top layer to an inner layer late in routing “to reduce EMI.” Same width, same spacing, different impedance. Then the RF path needs a last-minute re-spin, or the high-speed link starts reflecting at connectors.

If you need a quick sanity rule: don’t swap microstrip ↔ stripline without re-solving impedance (field solver or fab stackup table). Treat it like changing the connector footprint—because electrically, it is.

Dielectric thickness to the reference plane: the biggest impedance knob

The distance from trace to its reference plane (often called H) is one of the biggest levers for impedance:

- Bigger H → weaker coupling to the plane → higher impedance

- Smaller H → stronger coupling → lower impedance

Stackup decides H through core/prepreg selection, layer order, and whether a plane sits directly under the signal layer.

Where projects go sideways:

- Someone chooses a “standard” stackup for lead time, but the dielectric thickness under the critical layer isn’t what the designer assumed.

- Or the fab tweaks prepreg style to hit lamination targets, and impedance drifts unless you specified controlled impedance with coupons.

If your goal is controlled impedance, lock these early:

- target impedance (single-ended / differential)

- which layer the net lives on

- target dielectric thickness to the reference plane

- copper weight assumptions (because thickness affects geometry)

Dielectric constant (Dk) and dissipation factor (Df): material choice at high frequency

At low-ish frequencies, FR-4 often “works.” At higher frequencies, material becomes a performance dial:

- Dk (dielectric constant) influences impedance and propagation delay.

- Df (dissipation factor / loss tangent) drives dielectric loss, which eats margin on long channels.

Two boards can both be “50 Ω,” yet one has noticeably higher insertion loss because of higher Df. That’s why RF and high-speed digital teams talk about loss budget, not just impedance targets.

Practical scenario:

- You prototype on FR-4, then shift to an RF laminate for production. Dk changes, so your old width/spacing no longer lands on the same impedance. If you don’t re-size geometry, your “drop-in material swap” turns into a tuning session.

For mixed-signal products, a common compromise is:

- use cost-effective FR-4 where it’s safe

- use higher-performance materials only for the RF / fastest lanes

- keep the transition zones short and well-referenced

Reference planes and return path continuity: where impedance calculations break

Impedance calculators assume a clean, continuous return path. High frequency return current hugs the signal path, mainly under the trace on the reference plane.

So, stackup choices that improve return paths usually improve impedance behavior:

- dedicated solid ground planes near critical layers

- symmetric plane distribution to reduce warpage and keep geometry stable

- consistent reference for long runs (avoid reference hopping)

Classic failure mode: routing across a split plane, a moat, or an isolated copper island. The return current detours. That detour changes inductance, creating an impedance discontinuity you didn’t model.

If you’re doing bring-up on a flaky high-speed link, check the plane story first:

- Does the signal reference a solid plane the whole way?

- Do stitching vias keep the return path tight at layer transitions?

- Did someone “clean up ground” and accidentally carve a gap under the lane?

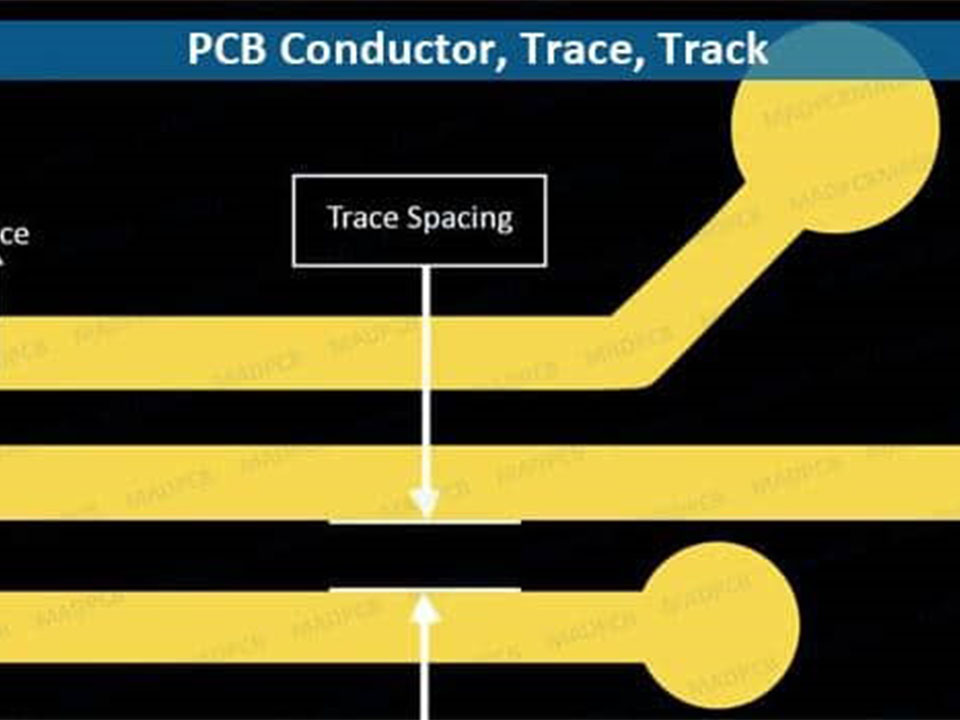

Copper pour clearance and crosstalk: nearby copper pulls impedance

Copper around a controlled-impedance trace isn’t neutral. Copper pours, guard traces, and adjacent layers can reshape fields and “pull” impedance.

What that looks like in production:

- A designer hits 50 Ω on the bare trace.

- Then a ground pour gets added close to the line “for shielding.”

- The effective capacitance increases, impedance drops, and the match shifts.

This is why RF teams like coplanar waveguide with ground (CPWG) only when they intentionally model it. If you add side copper accidentally, you create a CPWG-like structure without solving it.

Also watch coupling:

- tight diff pair spacing changes impedance and crosstalk tradeoffs

- dense HDI routing can bring aggressors too close on adjacent layers

When density is high, treat clearance rules as electrical constraints, not cosmetic layout style.

Manufacturing tolerances: why controlled impedance needs a locked stackup

Even a perfect field-solved design can drift in the real factory because impedance depends on variables that move:

- etch width variation (over/under-etch)

- dielectric thickness variation (prepreg flow, glass style)

- copper thickness variation (plating, foil, surface finish stack)

That’s why serious controlled-impedance builds use:

- impedance coupons

- TDR validation

- etch compensation

- clear callouts for impedance tolerance and which nets are controlled

Translation: if you need predictable impedance at high frequency, don’t just “target 50 Ω.” Specify the control method and let the fab tune the process inside their tolerance window.

Stackup choices vs impedance impact at high frequency

| Stackup choice (keyword) | What changes in impedance behavior | What you’ll see on the bench | What to do in DFM / fab notes |

|---|---|---|---|

| Microstrip vs stripline | Different field environment → different Z0 and velocity | RF match shifts, diff pair skew surprises | Lock layer assignment; re-solve when moving layers |

| Dielectric thickness (H) | H shifts Z0 strongly | Reflections at connectors, eye margin loss | Specify target H; approve a fab stackup |

| Dk / Df material selection | Dk affects geometry; Df affects loss | More attenuation, less margin, noisy edges | State material family; align with loss budget |

| Reference planes continuity | Return path detours create discontinuities | EMI spikes, random link errors | Avoid plane splits; add stitching vias |

| Copper pour clearance | Nearby copper increases coupling, lowers Z0 | “Works until pour added” failures | Keep clearance or model CPWG intentionally |

| Tolerances + etch comp | Real geometry differs from nominal | Lot-to-lot variation, yield issues | Use coupons + TDR; allow fab tuning |

Practical high-frequency scenarios that stackup can make or break

RF front-end and antenna feed (impedance matching, CPWG, via transitions)

RF traces don’t forgive stackup drift. A small impedance shift can move your match, which shows up as range loss, sensitivity drop, or unstable PA behavior. In RF builds, teams often:

- keep the feedline topology consistent (microstrip or CPWG)

- control reference planes tightly

- minimize layer swaps and via stubs

If you’re building RF prototypes or high-frequency boards, it’s worth aligning stackup and impedance control early through a dedicated high-frequency PCB workflow, not as a late-stage patch. You can route readers to your RF and high-frequency capability pages for this path (see links below).

High-speed digital interfaces (SERDES, USB, HDMI, Ethernet, DDR)

Digital teams sometimes underestimate how fast edges “act RF.” The stackup decisions that keep impedance stable also reduce EMI and simplify compliance:

- solid reference planes

- consistent layer usage for critical lanes

- short, well-stitched layer transitions

- controlled pair geometry with clear constraints

If your deliverable includes assembly, signal integrity issues can turn into expensive rework loops. That’s why many OEM and EMS teams prefer to pair controlled-impedance fabrication with turnkey build flow.

HDI and fine-pitch BGA escape (dense routing, coupling, yield)

HDI stackups squeeze geometry. That boosts sensitivity to process variation and coupling. The trick is balancing:

- routing density vs impedance stability

- via strategy vs stubs

- plane placement vs escape routing

In practice, you solve this by treating stackup as a first-class design object, not a table you pick at the end.

Where this fits our manufacturing flow (B2B prototyping → volume → assembly)

If you’re sourcing from a China-based B2B PCB factory, the fastest way to reduce risk is simple:

- decide the stackup early

- call out controlled impedance clearly

- let DFM + coupon/TDR close the loop before you scale

If you want to align the article with your site structure, here are internal pages that match the typical buyer journey and the technical topics above (all links pulled from your PCB.json list).

- Start at the homepage for the full overview: China PCB B2B factory: fast prototyping, reliable assembly

- For controlled builds and layer planning: PCB capabilities

- For controlled-impedance board builds and stackup choices: Advanced PCB services

- For build scope on bare board manufacturing: PCB fabrication service

- For turnkey builds that need SI-friendly assembly: PCB assembly service

- For quality gates that matter on controlled impedance: Quality control

- For project fit and supplier evaluation: About us

- For inquiries and DFM handoff: Contact us

If you want this piece to be even more “shop-floor useful,” share one target (for example: 50 Ω single-ended microstrip, or 100 Ω differential stripline) plus your preferred layer count. I can rewrite the scenarios to match that exact stackup style without stuffing in filler text.

MC PCB.,Ltd, alongside Dongguan MaoChang Printed Circuit Board Limited,has focused on PCB manufacturing over 20 years. MaoChang Printed Circuit Board Limited, a professional PCB factory for Quick Turn PCB, Prototype PCB and High Mix Low Volume fabrication. With UL certification for Rigid FR-4 / High Frequency / Aluminum Based PCB production.

Company

Products

Contact